# Simulation and Modeling of Self-Heating Effects in Heterojunction Bipolar Transistors

Chhandak Mukherjee<sup>\*</sup>, C. K. Maiti

Department of Electronics & Electrical Communication Engineering, IIT Kharagpur, India

\*chhandakkgp@gmail.com

*Abstract-* In this work, we investigate the self-heating effects on n-p-n Si heterojunction bipolar transistors (HBTs) with SiGe base and AlGaAs/GaAs HBTs with graded GaAs base via Technology CAD (TCAD) simulation study. Using fully coupled energy balance coupled with thermionic emission transport, two-dimensional numerical process and device simulations have been performed. It is observed that both the self-heating and local temperature increase due to higher internal device power dissipation. Dependence of direct current (DC), alternating current (AC) and self-heating effects on alloy composition of SiGe in the base region are investigated. It is shown that the self heating in SiGe HBTs is high (compared to identical Si BJTs) and significant electrical performance degradation takes place in SiGe HBTs.

Keywords- HBT; SiGe; GaAs; AlGaAs; TCAD; Self-Heating; Energy Balance; Device Simulation; Process Simulation

### I. INTRODUCTION

Strain-engineering has recently been the key technology governing the phenomenal growth of semiconductor industries due to strain-induced enhancement in device performance [1, 2]. With the advent of BiCMOS technology, design and fabrication of strain-engineered heterojunction bipolar transistors have also been possible. High-speed BiCMOS technology involves Si/Si<sub>1-x</sub>Ge<sub>x</sub>/Si HBTs, which is integrated within the conventional CMOS process. Electrical performances of SiGe HBTs mainly depend on physical parameters in the compressively strained SiGe base [3]. Extensive modelling efforts have been made for the proper description of the HBT operation, including appropriate mobility and lattice heating. Rosenfeld et al. [4, 5] have described the virtual substrate (VS) HBT using classical one-dimensional (1-D) drift-diffusion (DD) quasi-static analytical models which were applied for calculating the regional carrier transit times. However, the drawbacks of application of the DD for small geometry devices are well known and for very narrow-base HBTs, the computed base transit time is overestimated as velocity overshoot effects are not included [6]. Also, two-dimensional (2-D) transport effects are required for more accurate device analysis as the SiGe HBTs mainly operate in the high-injection regime. In the present study, we used 2-D numerical process and device simulation for Si/SiGe/Si structures. A full energy-balance (EB) transport model coupled with thermionic emission and Fermi-Dirac statistics were employed in our simulations using a commercial TCAD tool [7]. Effects of self-heating were studied using the non-isothermal EB model. Also, a different HBT architecture with AlGaAs emitter and GaAs base has been studied following a similar approach. In this work, we discussed the results of DC, high frequency and self-heating characteristics obtained for HBTs with SiGe base and AlGaAs/GaAs with graded GaAs base.

#### II. DEVICE STRUCTURE

HBT device structures used in ATLAS [7] simulation were generated using process simulator ATHENA [7] following the typical process flow [8, 9].

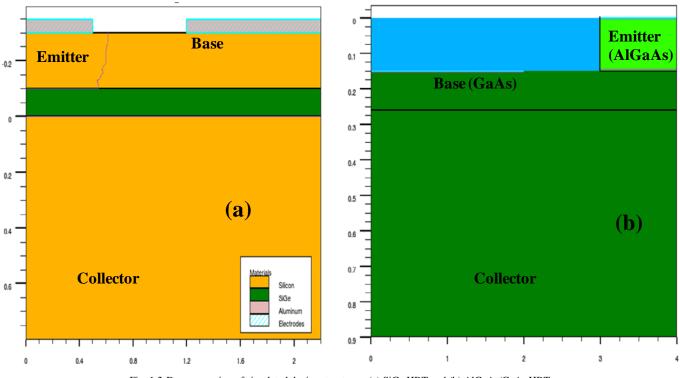

## A. The Si/SiGe HBT

A single poly-silicon (with a peak doping concentration of  $5 \times 10^{19}$  cm<sup>-3</sup>) vertical n-p-n SiGe HBT device structure with dual self-aligned base contacts was adopted for the simulation study. A constant Ge-profile is kept in the highly doped narrow p-type base as it has been stated that a constant Ge composition produces the same neutral base transit time as a graded Ge profile as long as the effective base Gummel numbers of the two are equal [10]. Our current study is comparative in nature, which suffices the use of a constant Ge profile in the base. Due to the device symmetry, only half of the device structure was simulated as shown in Fig. 1 (a). The peak doping concentrations in the base and total base width after HBT processing were  $2 \times 10^{18}$  cm<sup>-3</sup> and 0.15 µm, respectively. In addition, the SiGe HBT shows an early voltage of 11 V as extracted from the simulated output characteristics.

## B. The AlGaAs/GaAs HBT

The AlGaAs/GaAs HBT, similar to the SiGe HBT, is an n-p-n vertical bipolar transistor structure with AlGaAs emitter having a graded alloy composition profile at the bottom of the region near the base-emitter junction. A peak concentration of  $1 \times 10^{19}$  cm<sup>-3</sup> is achieved in the highly-doped p-type GaAs base region of width 0.1 µm. The AlGaAs HBT shows a very high early voltage of 80 V compared with the SiGe HBT. The simulated AlGaAs/GaAs HBT structure is shown in Fig. 1 (b).

Fig. 1 2-D cross-section of simulated device structures; (a) SiGe HBT and (b) AlGaAs/GaAs HBT

#### III. NUMERICAL MODELING

For accurate simulation, the physical models in ATLAS [7] were calibrated with the material parameters of SiGe, GaAs and AlGaAs. Standard values of the conduction and valence band discontinuity at the strained-Si<sub>1-x</sub>Ge<sub>x</sub>/ Si heterojunctions were used and the corresponding heterojunction band alignments were adjusted by the electron affinities. For the band gap, permittivity and affinity of SiGe, GaAs and AlGaAs alloys with different alloy composition, default values of the device simulator (ATLAS) were used [7]. As for carrier transport parameters, the Klaassen mobility model [11] was used. Fitting parameters were chosen to adjust the model for SiGe, GaAs and AlGaAs layers according to the mobility data for the respective materials [12-20]. It includes the increase of hole mobility with strain, and the decrease of electron mobility due to alloy scattering. In the SiGe HBT, the low-doping electron and hole lifetimes were set to 10<sup>-7</sup> s for Si and 10<sup>-8</sup> s for SiGe, and their falloffs with increased doping were assumed to follow the carrier lifetime models for silicon in ATLAS [7]. The lifetimes in the AlGaAs/GaAs HBT will be  $2 \times 10^{-10}$  s with the energy balance mode activated (including the parameters TAUREL.EL and TAUREL.HO) and temperature dependence of the electron and hole relaxation times (TAUMOB.EL, and TAUMOB.HO) included. Finally, as for the band-gap narrowing (BGN) effects, the numerical device simulator we have currently used attributes the whole band-gap reduction to a majority carrier band only. It neglects the effect of BGN distribution between conduction and valence band, which involves a certain inaccuracy in predicting realistic device currents, which will depend on the employed analytical BGN model. In the current study, we have used a built-in standard Slotboom and de Graaff BGN model in ATLAS [7] for all HBT simulations specifying BGN.E, BGN.N, and BGN.C parameters in the MATERIAL statement, yielding moderate simulation error, but neglecting influence of strain on the BGN. Device simulations employing a fully coupled energy balance (EB) model are time consuming and face convergence problems as a large number of mesh nodes is required for higher accuracy of the simulation. The conventional drift-diffusion (DD) model of charge transport neglects non-local transport effects such as velocity overshoot, diffusion associated with the carrier temperature and the dependence of impact ionization rates on carrier energy distributions. These phenomena can have a significant effect on the terminal properties of submicron devices. In the device simulator, ATLAS, two non-local models of charge transport, the energy balance, and hydrodynamic models are used [7]. The EB transport model follows the derivation by Stratton [21, 22] which is derived from the Boltzmann Transport Equation. The EB transport model adds continuity equations for the carrier temperatures, and treats mobilities and impact ionization coefficients as functions of the carrier temperatures rather than functions of the local electric field [7]. The EB model introduces two new independent variables  $T_n$  and  $T_p$ , the carrier temperature for electrons and holes. The energy balance equations consist of an energy balance equation with the associated equations for current density and energy flux  $S_{n,p}$ . The EB model for electron is represented below:

$$div\overline{S_n} = \frac{1}{q} \overline{J_n} \cdot \vec{E} - W_n - \frac{3k}{2} \frac{\partial}{\partial t} (\lambda_n * nT_n)$$

$$\overline{J_n} = qD_n \nabla n - q\mu_n n \nabla \psi + qnD_n^T \nabla T_n$$

$$\overline{S_n} = -K_n \overline{\nabla} T_n - \left(\frac{k\delta_n}{q}\right) \overline{J_n} T_n$$

$$(1)$$

where  $\overline{S_n}$  is the energy flux density associated with electrons, and  $\mu_n$  is the electron mobility. Among the remaining terms,  $D_n$  is the thermal diffusivity for electron;  $W_n$  is the energy density loss rates for electrons;  $K_n$  is the thermal conductivity of electrons [7]. In our simulations, the EB model was used and hot carrier transport equations were activated by setting the EB simulation flags HCTE.EL in the MODEL statement, specifying that the electron temperature will be solved.

The self-heating simulations are incorporated in the HBT structures using GIGA, which enables ATLAS to account for lattice heat flow and general thermal environments [7]. GIGA implements Wachutka's thermodynamically rigorous model of lattice heating [23], which accounts for Joule heating, heating, and cooling due to carrier generation and recombination, and the Peltier and Thomson effects. GIGA accounts for the dependence of material and transport parameters on the lattice temperature. GIGA also supports the specification of general thermal environments using a combination of realistic heat-sink structures, thermal impedances, and specified ambient temperatures. GIGA works with both S-PISCES (for Si-based devices) and BLAZE (for compound semiconductor devices) and with both the DD and EB transport models [7]. When simulating including the self-heating effects, GIGA adds the heat flow equation to the primary equations that are solved by ATLAS. The heat flow equation has the following expression [7]:

$$C\frac{\partial T_L}{\partial t} = \nabla(\kappa \nabla T_L) + H \tag{2}$$

Where C is the heat capacitance per unit volume,  $\kappa$  is the thermal conductivity, H is the heat generation,  $T_L$  is the local lattice temperature. The ATLAS built-in lattice thermal models were calibrated in our present study. We have included the lattice heat flow equation in ATLAS simulations specifying the LAT. TEMP parameter in the MODELS statement, for comparing with results from the simulations with the lattice heating effect turned off. In our HBT simulations, both HCTE and LAT.TEMP parameters are specified in the MODELS statement and both particle continuity equations are solved. Additionally, in our simulations including the self-heating effects, we have used a non-isothermal energy balance model. In GIGA, the electron and hole current densities are modified to account for spatially varying lattice temperatures and the electron and hole currents are represented as:

$$\overline{J_n} = -q\mu_n n \left( \nabla \phi_n + P_n \nabla T_L \right)

\overline{J_p} = -q\mu_p p \left( \nabla \phi_p + P_p \nabla T_L \right)$$

(3)

Where  $P_n$  and  $P_p$  are the absolute thermoelectric powers for electrons and holes, respectively [7]. The heat capacity of SiGe alloys was taken to be the same as that of Si, since the specific heat of pure Si and Ge differs by less than 5% for T > 300 K [24]. The values of the thermal conductivity,  $\kappa$ , as shown in Eq. (2), are specified in the MATERIAL statement using three user specifiable parameters, i.e., TC.A, TC.B, TC.C; thermal conductivity is generally temperature dependent. The values of these parameters for different materials used in our simulation are specified in Table 1. The contacts were modelled in ATLAS [7] as internal thermal contacts with externally attached thermal conductivities to a thermal sink held at 300 K using the THERMCONTACT statement. With the external thermal conductivities accounting for the HBTs extrinsic regions and packaging, a more realistic temperature distribution within the simulated device is obtained as suggested by Grasser et al. [25]. The THERMCONTACT statement also specifies the parameter ALPHA which accounts for the inverse value of thermal resistance in W/ (cm<sup>2</sup>.K). The value of ALPHA is set to 1500 in our simulations.

TABLE 1 THREE THERMAL CONDUCTIVITY COEFFICIENTS FOR DIFFERENT MATERIALS

| Materials        | Thermal Conductivity Coefficients |      |      |

|------------------|-----------------------------------|------|------|

|                  | TC.A                              | TC.B | TC.C |

| Si               | 0.7                               | 0    | 0    |

| SiGe             | 2.5                               | 0    | 0    |

| GaAs             | 2.27                              | 0    | 0    |

| AlGaAs           | 7.9                               | 0    | 0    |

| SiO <sub>2</sub> | 10 <sup>4</sup>                   | 0    | 0    |

#### IV. RESULTS AND DISCUSSIONS

## A. Si/SiGe HBT

#### 1) DC Characteristics

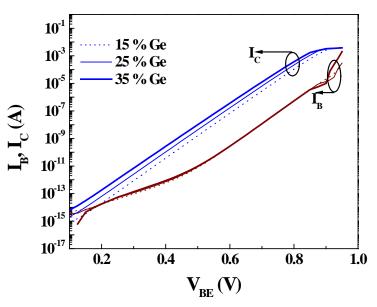

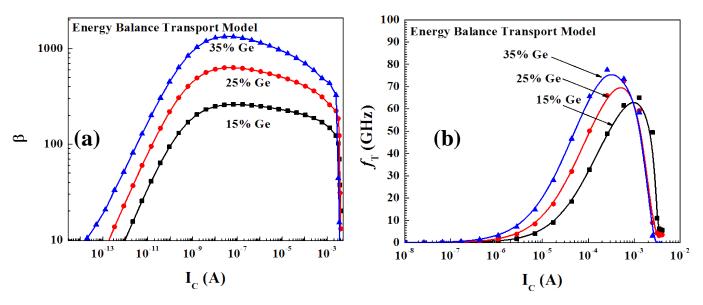

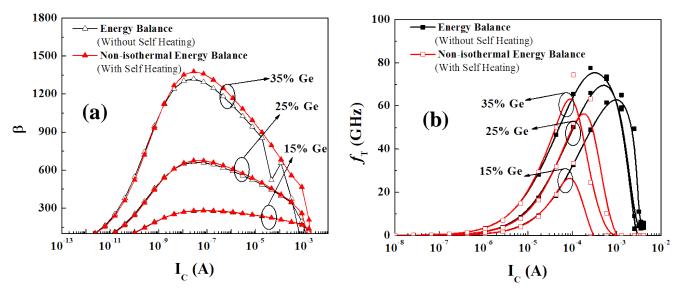

Fig. 2 shows Gummel plots of Si/Si<sub>1-x</sub>Ge<sub>x</sub>/Si HBTs simulated for a constant (box) Ge profile in the base. By reducing Ge composition, different values of maximum dc current gain  $\beta_{max}$  of 1350, 670 and 280, are obtained for HBTs with Ge fractions as 35%, 25% and 15%, respectively. This change in the current gain is attributed to the physical models causing change in carrier mobility due to the change in Ge composition in the base. Fig. 3 shows the corresponding current gain,  $\beta$ , and cut-off frequency,  $f_T$ , as a function of the collector current at different Ge compositions. The peak cut-off frequency recorded for a Ge fraction of 35% was 80 GHz. It is observed that due to the increase in carrier mobility in the base and the increased Ge fraction, the current gain increases substantially. The cut-off frequency also increases due to the reduction of the base transit time caused by higher carrier mobility in the base.

Fig. 2 Gummel plot of /SiGe/Si HBTs at three different Ge fractions in SiGe base

Fig. 3 (a) Current gain,  $\beta$  and (b) unity gain cut-off frequency,  $f_T$  as a function of collector current for different Ge compositions in the base

## 2) Self-heating Characteristics

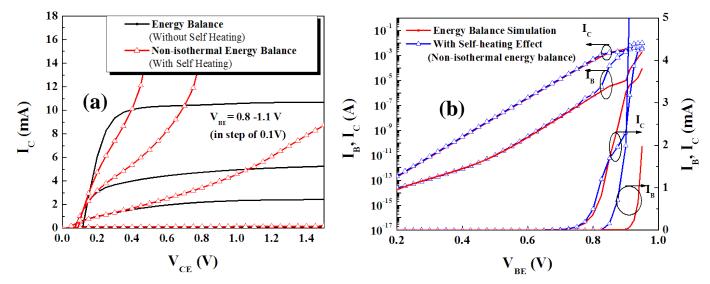

HBTs usually operate at high-current densities for availing maximum working frequencies. Increased power dissipation within the device results in lattice self-heating, which degrades the electrical performances significantly, such as the early voltage of the HBT. The average thermal conductivity of the SiGe alloy is significantly lower than that of the Si [26] and is a

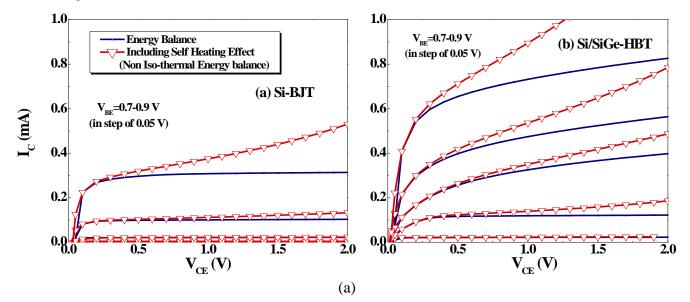

function of the alloy composition, down to a minimum with the Ge fraction in the range of 20-50%. It also decreases with the increase of impurity concentration due to the increased scattering by dopants [24]. In Fig. 4 (a), the output characteristics are shown for the simulated SiGe HBT using GIGA (ATLAS) [7], comparing the collector currents with and without the self-heating effects (non-isothermal), with the energy balance model activated in both cases. The corresponding Gummel plot for the SiGe HBT is shown in Fig. 4 (b), revealing the increased slope of base and collector currents due to the self-heating. Fig. 5 shows a decrease in the current gain of the SiGe HBT due to the self-heating effect. Additionally, substantial degradation is observed in the unity gain cut-off frequency due to a prominent thermal degradation, owing to the poor thermal conductivity of the SiGe base, thereby increasing the base transit time.

Fig. 4 Comparison of (a) output characteristics and (b) Gummel plot of SiGe HBT with and without self-heating effects

Fig. 5 Comparison of (a) current gain,  $\beta$  and (b) unity gain cut-off frequency,  $f_T$  with and without self-heating effects

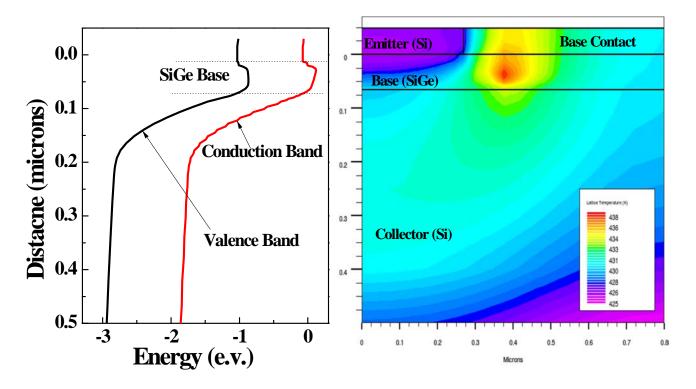

In Fig. 4, substantial degradation is observed in the early voltage due to self-heating in the SiGe HBT. The simulated 2-D temperature distribution of the SiGe HBTs is shown in Fig. 6 with the energy band diagram of the device, depicting the conduction and valence band energies along the depth of the vertical HBT. Although 2-D lattice-heating simulation tends to overestimate the actual device internal temperature [25], the simulation reveals a peak temperature of 438 K. Hot-spot formation is observed in the HBT due to the emitter injection current crowding, causing local heating at the emitter edge [27]. The self-heating effects are further enhanced in the SiGe HBTs with the increasing base Ge content due to the increase in SiGe alloy thermal resistance [26].

Fig. 6 (a) Energy band diagram of the SiGe HBT, (b) 2-D temperature profile in a SiGe HBT. A peak lattice temperature of 438 K is observed.

## 3) Comparison of Self-heating in SiGe HBT and Si BJT

A comparison is made between the self-heating in a SiGe HBT (simulated using a similar structure depicted in Fig. 1) and a Si BJT with identical dimensions and doping conditions as shown in Fig. 7. The 2D temperature profile of the simulated device structures shown in Fig. 7 (b) indicates that a peak temperature difference of 90K exists between the SiGe HBT and the identical Si BJT for the same power dissipation. In addition, the output characteristics reveal that the early voltage degradation is more apparent in the SiGe HBT compared with the Si BJT as observed in Fig. 7 (a), suggesting more self-heating in SiGe HBT due to the presence of SiGe alloy. The results from Fig. 7 clearly show the need for special attention when dealing with the self-heating effects in SiGe HBTs.

(b)

Fig. 7 (a) Comparison of self-heating effects on the output characteristics of SiGe HBT and an identical Si BJT;

(b) Comparison of 2-D temperature profile due to self-heating in SiGe HBT and an identical Si BJT

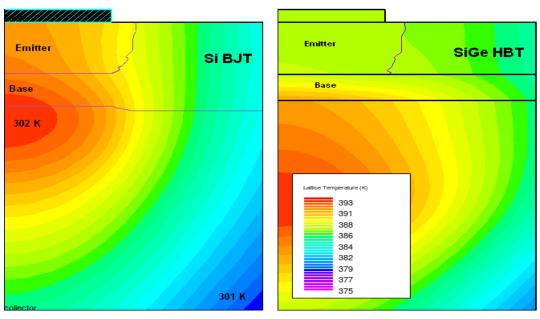

### B. Self heating in AlGaAs/GaAs HBT

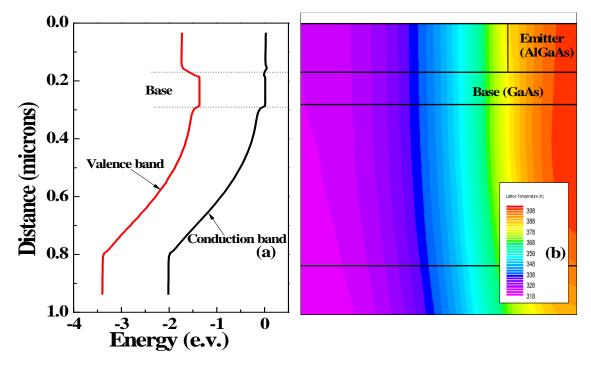

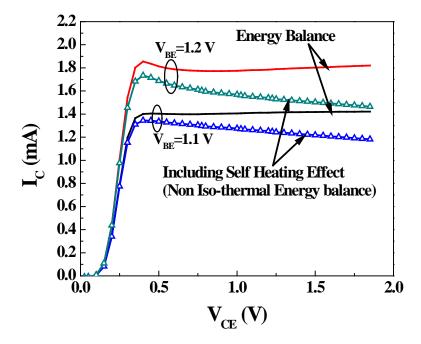

Fig. 8 shows the simulated structure of the AlGaAs/GaAs HBT obtained using GIGA (ATLAS) [7] depicting the energy band diagram (Fig. 8(a)) and the 2-D temperature profile (Fig. 8(b)). The temperature profile indicates a peak temperature of 398 K. The temperature profile observed in this case is somewhat different compared with the case of SiGe HBTs. Unlike the HBT temperature profile, the peak temperature in this case occurred near the collector region; the AlGaAs/GaAs HBT has a temperature profile in which the peak temperature is observed in the central region of the vertical structure (the 2D profile showing only the half of the structure) covering both the emitter-base and base-collector junctions. In the former case, *i.e.* in SiGe HBT, the self-heating caused the degradation in the collector-base junction and the early voltage to show the increased slope of the output characteristics. In the AlGaAs/GaAs HBT, however, the output characteristics revealed a negative slope of the current due to the self-heating, as shown in Fig. 9.

Fig. 8 Simulated AlGaAs/GaAs HBT structure showing (a) the energy band diagram and (b) the 2-D temperature profile

Fig. 9 Output characteristics of AlGaAs/GaAs HBT with and without self-heating effects; a negative slope is observed in the output characteristics due to lattice heating

The negative slope of the output characteristics is the effect of a negative resistance as observed in Fig. 9, due to the self-heating in the HBT. When electrical power is dissipated in a solid-state device, the temperature inside the device should increase correspondingly. This increase in temperature affects the device characteristics, which, in turn, can lead to an alteration in the dissipated power within the device. The whole process forms a thermo-electrical feedback loop. The feedback can be positive or negative for different operating conditions. One familiar example is thermal runaway in BJTs, where a positive feedback loop leads to an uncontrolled increase in the junction temperature. Since HBTs can carry high current with very high current density in a small emitter area, and bearing in mind the low thermal conductivity of the GaAs substrate, the AlGaAs/GaAs HBTs can experience severe local heating. Often is the case that the HBT output characteristics show a negative slope in the high current region, as observed in our case in Fig. 9 with self-heating simulation of the AlGaAs HBT, which might be expected to cause stability problems at low frequencies. The negative slope in AlGaAs/GaAs is reported by other studies as well [28-30]. We can assume that the negative resistance is caused due to the local heating of the base-emitter junction of the HBT which may lead to the high-injection of carriers due to thermal agitation across the emitter-base junction, leading to a large base current where the thermal effect becomes prominent. The uneven increase of  $I_B$  and  $I_C$  with the increase of  $V_{CB}$  or  $V_{CE}$  leads to this phenomenon. The increased  $I_B$ , due to the thermal effect, reduces the base-emitter voltage  $V_{BE}$  required to maintain the constant base current, which subsequently decreases the collector current.

#### V. CONCLUSIONS

A comprehensive TCAD study of both Si/SiGe/Si and AlGaAs/GaAs NPN HBTs is presented. A full energy balance model coupled with a thermionic emission transport model was used in 2-D numerical device simulations of vertical HBT structures. In SiGe HBTs, DC Gummel plot revealed the increase in base and collector currents with Ge fraction in the SiGe base. From high-frequency simulation, based on the simulated small-signal current gain and unilateral power gain frequency dependences, the unity gain cut-off frequencies were extracted for different alloy compositions. In addition, numerical device simulation including lattice heating revealed that self-heating effects severely degrade the device characteristics such as the early voltages of SiGe HBTs owing to the poor thermal conductivity of SiGe alloy layers. The current gain and the cut-off frequencies also suffer prominent degradation due to the self-heating. Comparison with identical BJT reveals that the early voltage degradation is more apparent in the SiGe HBT due to a more prominent self-heating. AlGaAs/GaAs HBTs also reveal self-heating induced degradation. In our study, it was observed that the self –heating caused a negative resistance, thereby resulting in a reduced collector current in the high-current regime and displaying a negative slope in the output characteristics. In conclusion, the simulation study presented in this paper revealed some major reliability issues arising from lattice heating that need addressing while designing high performance HBTs for applications in future Bi-HCMOS technologies.

#### REFERENCES

- A. G. O'Neill and D. A. Antoniadis, "Deep submicron CMOS based on silicon germanium technology," *IEEE Trans. Electron Dev.*, vol. 43, pp. 911-918, June 1996.

- [2] S. G. Badcock, A. G. O'Neill and E. G. Chester, "Device and circuit performance of SiGe/Si MOSFETs," Solid-State Electron, vol. 46,

pp. 1925-1932, 2002.

- [3] D. L. Harame, D. C. Ahlgren, D. D. Coolbaugh, J. S. Dunn, G. G. Freeman and J. D. Gillis, *et al.*, "Current status and future trends of SiGe BiCMOS technology," *IEEE Trans. Electron Dev.*, vol. 48, pp. 2575-2594, November 2001.

- [4] D. Rosenfeld and S. A. Alterovitz, "The composition dependence of the cut-off frequencies of ungraded Si<sub>1-x</sub>Ge<sub>x</sub>/Si<sub>1-y</sub>Ge<sub>y</sub>/Si<sub>1-x</sub>Ge<sub>x</sub> HBTs," *Solid-State Electron*, vol. 38, pp. 641-651, March 1995.

- [5] D. Rosenfeld and S. A. Alterovitz, "High frequency performance of Si<sub>1-x</sub>Ge<sub>x</sub>/Si<sub>1-y</sub>Ge<sub>y</sub>/Si<sub>1-x</sub>Ge<sub>x</sub> HBTs," *IEE Electron Lett.*, vol. 29(3), pp. 260-261, February 1993.

- [6] C. Jungemann, B. Neinhus, and B. Meinerzhagen, "Comparative study of electron transit times evaluated by DD, HD, and MC device simulation for a SiGe HBT," *IEEE Trans. Electron Dev.*, vol. 48, pp. 2216-2220, October 2001.

- [7] "ATLAS User's Manual," SILVACO Inc., 4701 Patrick Henry Drive, Santa Clara, CA 95054, April 20, 2010.

- [8] G. A. Armstrong and C. K. Maiti, "TCAD for Si, SiGe and GaAs Integrated Circuits," *IET Circuits, Devices and Systems Series*, vol. 21, January 2007.

- [9] C. K. Maiti and G. A. Armstrong, "Applications of Silicon-Germanium Heterostructure Devices," Institute of Physics Publishing, Series in Optics and Optoelectronics Series, Taylor & Francis Group, 2001.

- [10] R. J. E. Hueting, J. W. Slotboom, A. Pruijmboom, W. B. De Boer, C. E. Timerinng and N. E. B. Cowern, "On the optimization of SiGebase bipolar transistors," *IEEE Trans. Electron Dev.*, vol. 43, pp. 1518-1524, September 1996.

- [11] D. B. M. Klaassen, "A unified mobility model for device simulation—I. Model equations and concentration dependence," *Solid-State Electron*, vol. 35, pp. 953-959, July 1992.

- [12] F. M. Bufler, P. Graf, B. Meinerzhagen, B. Adeline, M. M. Rieger and H. Kibbel, *et al.*, "Low- and high-field electron-transport parameters for unstrained and strained Si<sub>1-x</sub>Ge<sub>x</sub>," *IEEE Electron Dev. Lett.*, vol. 18, pp. 264-266, June 1997.

- [13] G. E. Stillman, C. M. Waife, and J. O. Dimmock, "Hall coefficient factor for polar mode scattering in n-type GaAs," J. Phys. Chem. Solids, vol. 31(6), pp. 1199-1204, 1970.

- [14] J. S. Blakemore, "Semiconducting and other major properties of gallium arsenide," J. Appl. Phys., vol. 53(10), pp. R123-R181, 1982.

- [15] D. L. Rode, Semiconductors and Semimetals, R. K. Willardson and A. C. Beer, eds., Academic Press, N.Y., vol. 10, pp. 1, 1975.

- [16] J. D. Wiley, Semiconductor and Semimetals, R. K. Willardson and A. C. Beer, eds., Academic Press, N.Y., vol. 10, pp. 91, 1975.

- [17] C. Hilsum, "Simple empirical relationship between mobility and carrier concentration," IEE Electron. Lett., vol. 10(13), pp. 259-260, 1974.

- [18] J. Pozhela and A. Reklaitis, "Electron transport properties in GaAs at high electric fields," *Solid State Electron*, vol. 23(9), pp. 927-933, September 1980.

- [19] H. D. Rees, "Hot electron effects at microwave frequencies in GaAs," Solid State Commun., vol. 7(2), pp. 267-269, February 1969.

- [20] V. L. Dalal, A. B. Dreeben, and A. Triano, "Temperature Dependence of Hole Velocity in p GaAs," J. Appl. Phys., vol. 42(7), pp. 2864-2867, 1971.

- [21] R. Stratton, "Diffusion of Hot and Cold Electrons in Semiconductor Barriers," Phys. Rev., vol. 126(6), pp. 2002-2014, 1962.

- [22] R. Stratton, "Semiconductor Current-Flow Equations (Diffusion and Degeneracy)," IEEE Trans. Electron Dev., vol. 19(12), pp. 1288-1292, 1972.

- [23] G. K. Wachutka, "Rigorous Thermodynamic Treatment of Heat Generation in Semiconductor Device Modeling," *IEEE Trans. Computer-Aided Design*, vol. 9(11), pp. 1141-1149, 1990.

- [24] J. P. Dismukes, L. Ekstrom, E. F. Steigmeier, I. Kudman and D. S. Beers, "Thermal and Electrical Properties of Heavily Doped Ge-Si Alloys up to 1300°K," J. Appl. Phys., vol. 35, pp. 2899-2907, 1964.

- [25] T. Grasser, R. Quay, V. Palankovski, S. Selberherr, "A Global Self-Heating Model for Device Simulation," Proc. IEEE 30<sup>th</sup> European Sol-State Dev. Research Conf. (ESSDERC), pp. 324–327, Cork, Ireland, 2000.

- [26] Y. S. Touloukian, R. K. Kirby, R. E. Taylor and T. Y. R. Lee, "Specific Heat, Metallic Elements and Alloys," *Thermophysical Properties of Matter*, vol. 4, New York (IFI/Plenum), 1970.

- [27] N. D. Jankovic and A. O'Neill, "Performance evaluation of SiGe heterojunction bipolar transistors on virtual substrates," *Solid-State Electron.*, vol. 48, pp. 277–284, 2004.

- [28] P. Baureis, D. Seitzer and U. Schaper, "Modeling of Self-heating in GaAs/AlGaAs HBTs for Accurate Circuit and Device Analysis," Proc. IEEE GaAs IC symp., pp. 125-128, 1991.

- [29] J. J. Liou, L. L. Liou and C. I. Huang, "Analytical model for the AIGaAs/GaAs multi emitter finger HBT including self-heating and thermal coupling effects," *IEE Proc.-Circuits Devices Syst.*, vol. 141(6), pp. 469-475, December 1994.

- [30] K. Lu, P. A. Perry, and T. J. Brazil, "A New Large-Signal AlGaAs/GaAs HBT Model Including Self-Heating Effects, with Corresponding Parameter-Extraction Procedure," *IEEE Trans. Microwave Theory and Techniques*, vol. 43(7), pp. 1433-1445, July 1995.

**Chhandak Mukherjee** was born in Kolkata, West Bengal, India in 1986. He received the B. E. degree in Electronics and Telecommunication engineering from the Jadavpur University, Kolkata, in 2008 and the M. Tech. degree in Microelectronics and VLSI Design from Indian Institute of Technology, Kharagpur, India, in 2010. Currently he is working towards his PhD in the area of semiconductor device modeling, low frequency noise characterization in strainengineered MOSFETs in the department of Electronics and Electrical Communication Engineering, Indian Institute of Technology, Kharagpur.From 2008 he has been working as a Teaching Assistant in the Semiconductor Process and Device Simulation laboratory in the Indian Institute of Technology, Kharagpur. He has co-authored two book chapters and more than 15 technical articles. His research interests include semiconductor device modeling, low-frequency noise characterization in semiconductor devices especially for strain-engineered and non-classical MOSFETs, FinFETs, nanowires, and tunneling spectroscopy studies of surface and interface.